CH347F 不需要配置工作模式,同时支持高速串口、I2C、SPI、JTAG 和 SWD 等接口。复用引脚的功能可通过驱动程序进行切换控制。

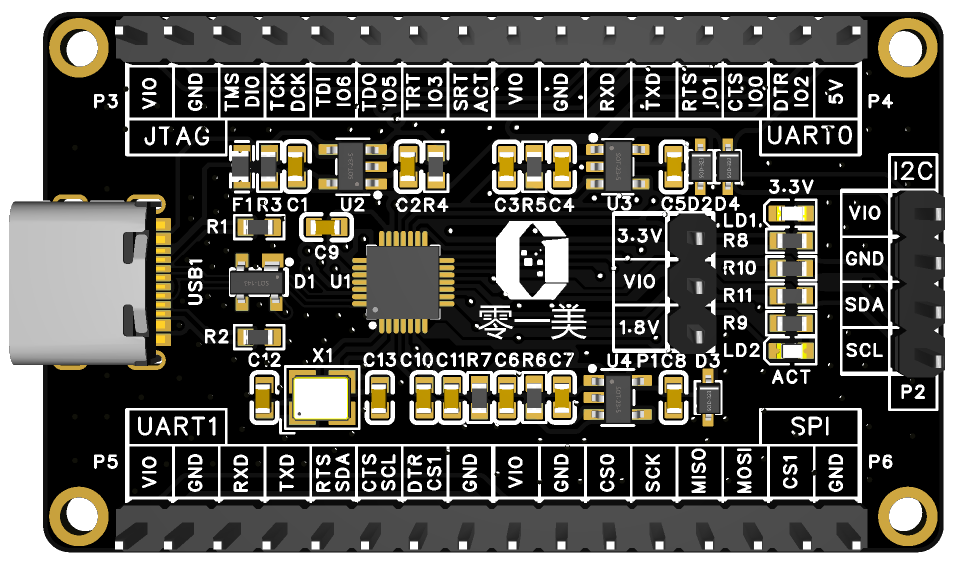

CH347F开发板的使用,主要集中在该开发板上的接口使用上。其主要包括以下7种接口,这些接口的位置详见图6-1所示。

P1为IO电源配置接口;P2为I2C同步串行通信接口;P3和P4、P5和P6中间的白色粗线是两种接口的分界线,上边16排针,左边8排针为JATG/SWD接口,右边8排针为UART0串行通信接口;下边16排针,左边8排针为UART1接口,右边8排针为SPI串行通信接口。

6.1.USB Type-C接口

图6-1中的USB1是用于和电脑连接的USB Type-C接口,支持正反插。通过USB Type-A转Type-C的连接线连接电脑和开发板。该USB Type-C接口包括USB电源和数据线,USB Type-C接口最大输入电流为500mA,即本电路板及其接口外接设备所需电流不得大于500mA,否则,本电路板USB接口的快慢过流保护电路会动作,导致无电源输出。

6.2.IO电源配置接口

图6-1中P1对应的1×3p 2.54mm间距排针是IO电源配置接口。VIO是连接CH347F芯片IO口电源的引脚。该接口可以通过短路块配置IO电源为1.8V或3.3V。若需要配置为2.5V,则需要VIO引脚外接2.5V电源。默认配置为3.3V。注意:虽然在1.8V和3.3V电源接口有过压(ESD)保护,但是,VIO引脚支持最大电压为3.3V,请勿超过该电压值,否则会导致该开发板内个别元件损坏,无法正常工作。

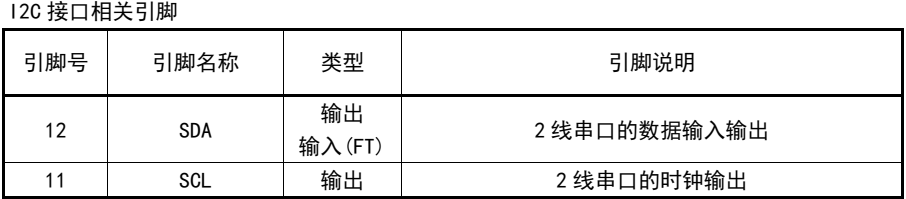

6.3.I2C通信接口

图6-1中P2是I2C串行通信接口,用于外接I2C 接口的芯片、模块或设备。该接口SDA和SCL在电路板上接有10kΩ上拉电阻,SDA和UART1接口的RTS复用,SCL同UART1接口的CTS复用,两则同时只能用其一。VIO是IO电源正极,一般为3.3V,GND为电源地。

CH347 芯片的 I2C/IIC 同步串行接口工作在 Host/Master 主机模式,包括 SCL 和 SDA 两根信号线。SCL 用于单向输出同步时钟,开漏输出,SDA 用于双向数据输入输出,开漏输出及输入。I2C 接口的基本操作元素包括:起始位、停止位、位输出、位输入。

(1)起始位定义为当 SCL 为高电平时,SDA 输出下降沿。

(2)停止位定义为当 SCL 为高电平时,SDA 输出上升沿。

(3)位输出定义为当 SCL 为低电平时,SDA 输出位数据,然后 SCL 输出高电平脉冲。

(4)位输入定义为当 SCL 输出高电平脉冲,在下降沿之前从 SDA 输入位数据。

CH347 芯片的 I2C 接口支持 5 种传输速度,通过计算机 API 配合,可灵活操作 2 线接口的 A/D、D/A、EEPROM 和传感器等器件。

6.4.JTAG/SWD接口

图6-1中的P3对应1×8p 2.54mm间距排针是JTAG/SWD接口。JATG、SWD和GPIO接口复用,3者只能同时用一种,其复用引脚为:

(1)CH347F芯片的9脚:JTAG接口的复位输出引脚TRST和GPIO3复用。

(2)CH347F芯片的23脚:SWD接口的时钟引脚SWDCLK、JTAG接口的时钟输出引脚TCK和GPIO4复用。

(3)CH347F芯片的24脚:JTAG接口的数据输入引脚TDO和GPIO5复用。

(4)CH347F芯片的25脚:JTAG接口的数据输出引脚TDI和GPIO6复用。

(5)CH347F芯片的26脚:SWD接口的数据引脚SWDIO、JTAG接口的模式选择引脚TMS和GPIO7复用。

CH347 芯片的 JTAG 接口工作在 Host/Master 主机模式。JTAG 接口包括 TMS、TCK、TDI、TDO、TRST(开发板上对应TRT)和 SRST (开发板上对应SRT)六根信号线,TRST 和 SRST 为可选信号线。支持自定义协议的快速模式和 bit-bang 模式,传输速率可达 30Mbit/S。提供计算机端的 USB 高速驱动和 USB 转 JTAG TAP 函数库,支持二次开发,用于构建自定义的USB转高速 JTAG 调试器、FPGA 下载器、CPU 编程器等产品。

CH347 芯片的 SWD 接口工作在 Host/Master 主机模式。SWD 接口包括 SWDCLK、SWDIO 两根信号线。提供计算机端的 USB 高速驱动和 USB 转 SWD 函数库,支持二次开发,用于构建自定义的 USB 转SWD 调试器、下载器等产品。

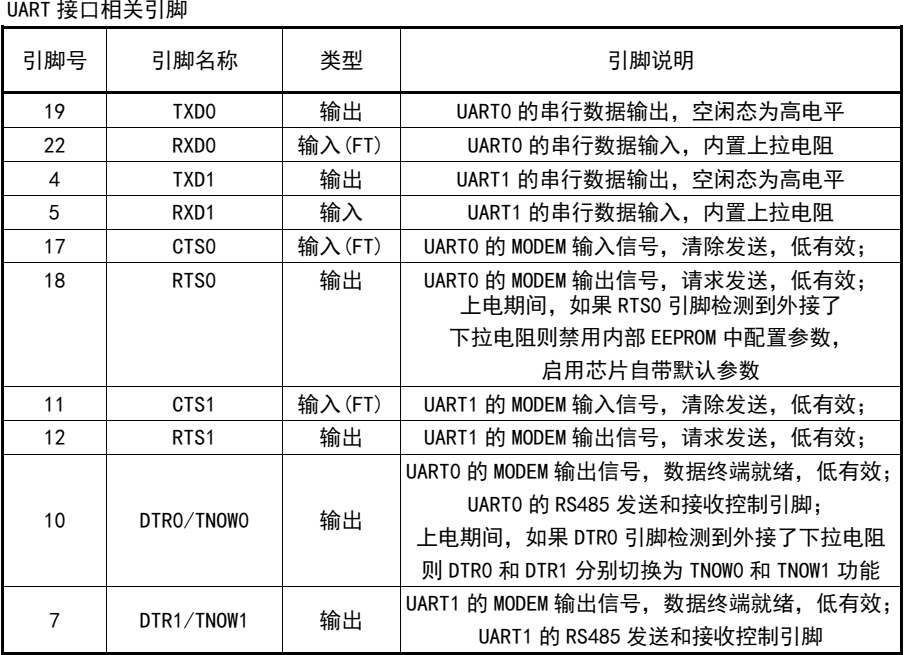

6.5.UART0和UART1串行通信接口

图6-1中的P4和P5对应1×8p 2.54mm间距排针是UART0和UART1异步串行通信接口。

UART0和UART1接口同I2C接口和GPIO口复用,引脚复用功能只能同时用一种,其复用引脚为:

(1)CH347F芯片的17脚:UART0接口的Modem输入信号引脚CTS和GPIO0复用。

(2)CH347F芯片的18脚:UART0接口的Modem输出信号引脚RTS和GPIO1复用。

(3)CH347F芯片的10脚:UART0接口的引脚DTR/TNOW和GPIO2复用。

(4)CH347F芯片的11脚:UART1接口的Modem输出信号引脚CTS和I2C接口的SCL复用。

(5)CH347F芯片的12脚:UART1接口的Modem输出信号引脚RTS和I2C接口的SDA复用。

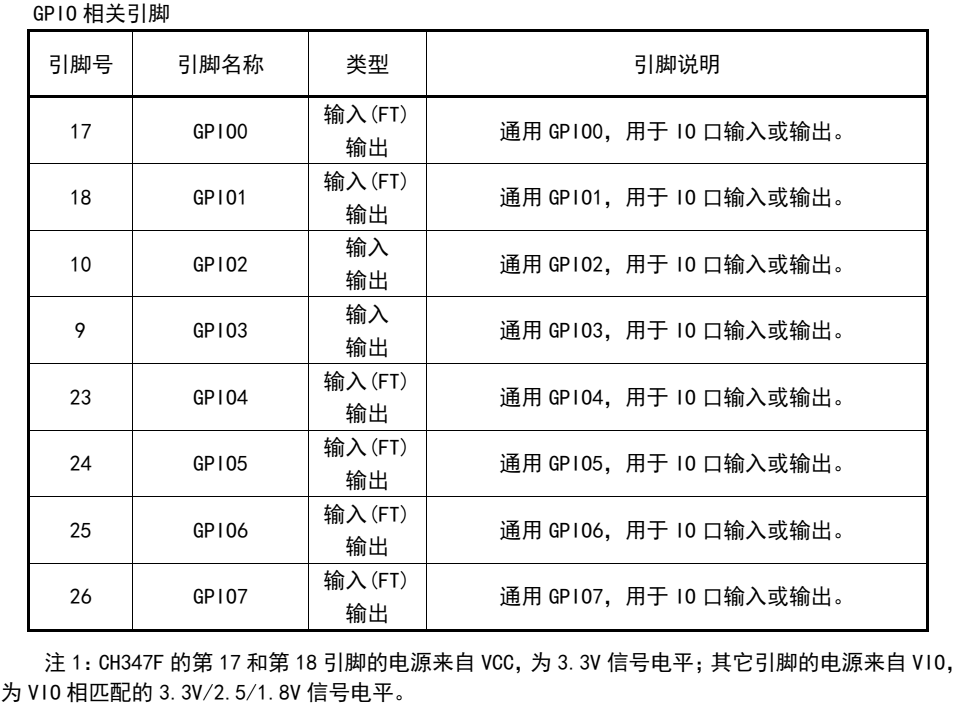

注意:CH347F 的第 17 和第 18 引脚的电源来自 VCC,为 3.3V 信号电平;其它引脚的电源来自 VIO,为 VIO 相匹配的 3.3V/2.5/1.8V 信号电平。

CH347F芯片提供2 组异步串口,每组串口包括 TXD、RXD、CTS、RTS、DTR 等引脚。串口 0支持全 MODEM 联络信号,串口 1 支持部分 MODEM 联络信号。

异步串口方式下CH347F芯片的引脚包括:数据传输引脚、MODEM 联络信号引脚和辅助引脚。

(1)数据传输引脚包括:TXD0、TXD1 和 RXD0、RXD1。串口输入空闲时,RXDx 为高电平,串口输出空闲时,TXDx 为高电平。

(2)MODEM 联络信号引脚和 RS485 发送和接收控制引脚:CTS0、RTS0、DTR0、CTS1、RTS1 和 DTR1。

CH347 芯片的串口内置了独立的收发缓冲区,支持单工、半双工或者全双工异步串行通讯。CH347 的串行数据包括 1 个低电平起始位、8 个数据位、1 个/2 个高电平停止位,支持无校验/奇校验/偶校验。

CH347F芯片的 2 个异步串口波特率最高支持 9Mbps。支持常用通讯波特率:1200、1800、2400、3600、4800、9600、14400、19200、28800、33600、38400、56000、57600、76800、115200、128000、153600、230400、460800、921600、1M、1.5M、2M、3M、4M、5M、6M、7M、8M、9M 等。

CH347F芯片的 2 个异步串口均支持 CTSx 和 RTSx 硬件自动流控制,默认不启用,可以通过 VCP 厂商驱动程序控制启用。如果启用,那么仅在检测到 CTSx 引脚输入有效(低电平有效)时串口才继续发送下一包数据,否则暂停串口发送;当接收缓冲区空时,串口会自动有效 RTSx 引脚(低电平有效),直到接收缓冲区的数据较满时,串口才自动无效 RTSx 引脚,并在缓冲区空时再次有效 RTSx 引脚。使用硬件自动速率控制,可以将己方的 CTSx 引脚接到对方的 RTSx 引脚,并将己方的 RTSx 引脚接到对方的 CTSx 引脚。

CH347F片串口接收信号的允许波特率误差不大于 2%,串口发送信号的波特率误差小于 1%。在计算机端的 Windows 操作系统下,安装高速率的 VCP 厂商驱动程序后,能够仿真标准串口,所以绝大部分串口应用程序完全兼容,通常无需任何修改。

CH347F芯片可以用于升级原串口外围设备,或者通过 USB 总线为计算机增加额外串口。通过外加电平转换器件,可以进一步提供 RS232、RS485、RS422 等接口。

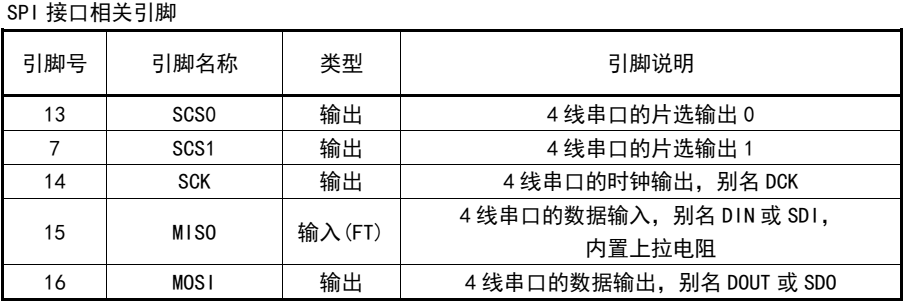

6.6.SPI同步串行通信接口

图6-1中的P6对应1×8p 2.54mm间距排针是SPI同步串行通信接口。

CH347F芯片的 4 线 SPI 同步串行接口工作在 Host/Master 主机模式,包括 SCSx、SCK(CLK)、MISO(SDI/DIN)和 MOSI(SDO/DOUT)四根信号线。SCSx 包括 SCS0 和 SCS1,可分时操作 2个 SPI 接口设备。

(1)支持 8 位/16 位数据结构。

(2)支持 MSB 和 LSB 传输。

(3)支持 SPI 模式 0/1/2/3。

(4)支持传输频率配置等。

(5)内置硬件 DMA,可进行批量数据的快速发送和读取。

通过计算机 API 配合,可灵活操作4线接口的 FLASH、MCU、传感器等器件。

6.7.GPIO接口

CH347F芯片支持最多 8 路 GPIO 输入输出控制功能。这8路GPIO同JTAT/SWD接口、UART0和UART1接口复用,同时只能使用一种功能,具体复用功能详见“6.4.JTAG/SWD接口”和“6.5.UART0和UART1异步串行通信接口”章节的内容。其需要配合驱动程序和相关操作函数才能使用该功能。沁恒公司提供的Demo程序中有关于GPIO操作的功能,详见“7.1.1.SPI/I2C/GPIO Debug标签页功能”章节内容。

最后编辑:谭鹏超 更新时间:2024-01-25 21:17